| Opcode |

Integer Arithmetic Instructions |

Details .=updateCR o=overflow c=carry e=extended

m=minus one z=zero as param (R0) |

R0=0? |

| addi rD,rA,SIMM |

Add Immediate |

The sum (rAID) + SIMM is placed into register rD.

|

Y |

| addis rD,rA,SIMM |

Add immediate shifted |

The sum (rA| 0) + (SIMM || x'0000') is placed into

rD. |

Y |

| add rD,rA,rB |

Add |

The sum (rA) + (rB) is placed into register rD.

add. rD,rA,rB addo rD,rA,rB addo. rD,rA,rB |

- |

| subf rD,rA,rB |

Subtract from |

The sum --. (rA) + (rB) + 1 is placed into rD

subf. rD,rA,rB subfo rD,rA,rB subfo. rD,rA,rB |

- |

| addic rD,rA,SIMM |

Add Immediate Carrying |

The sum (rA) + SIMM is placed into register rD.

addic. rD,rA,SIMM |

- |

| subflc rD,rA,SIMM |

Subtract from Immediate Carrying |

The sum --. (rA) + SIMM + 1 is placed into register

rD. |

- |

| addc rD,rA,rB |

Add Carrying |

The sum (rA) + (rB) is placed into register rD.

addc. rD,rA,rB addco rD,rA,rB addco. rD,rA,rB |

- |

| subfc rD,rA,rB |

Subtract from Carrying |

The sum -, (rA) + (rB) + 1 is placed into register

rD.

subfc. rD,rA,rB subfco rD,rA,rB subfco. rD,rA,rB |

- |

| adde rD,rA,rB |

Add Extended |

The sum (rA) + (rB) + XER(CA) is placed into

register rD.

adde. rD,rA,rB addeo rD,rA,rB addeo. rD,rA,rB |

- |

| subfe rD,rA,rB |

Subtract from Extended |

The sum -,(rA) + (rB) + XER(CA) is placed into

register rD.

subfe. rD,rA,rB subfeo rD,rA,rB subfeo. rD,rA,rB |

- |

| addme rD,rA |

Add to Minus One Extended |

The sum (rA) + XER(CA) + x'FFFFFFFF' is placed into

register rD.

addme. rD,rA addmeo rD,rA addmeo. rD,rA |

- |

| subfme rD,rA |

Subtract from Minus One Extended |

The sum..., (rA) + XER(CA) + x'FFFFFFFF' is placed

into register rD.

subfme. rD,rA subfmeo rD,rA subfmeo. rD,rA |

- |

| addze rD,rA |

Add to Zero Extended |

The sum (rA) + XER(CA) is placed into register rD

addze. rD,rA addzeo rD,rA addzeo. rD,rA |

- |

| subfze rD,rA |

Subtract from Zero Extended |

The sum..., (rA) + XER(CA) is placed into register

rD.

subfze. rD,rA subfzeo rD,rA subfzeo. rD,rA |

- |

| neg rD,rA |

Negate |

NEGate register rA, and store the results in

register rD. This converts a positive to a negative and vice

versa.

neg. rD,rA nego rD,rA nego. rD,rA |

- |

| Opcode |

Integer Compare Instructions |

Details .=updateCCR o=Overflow |

|

| mulli rD,rA,SIMM |

Multiply Low Immediate |

The low-order 32 bits of the 48-bit product

(rA)*SIMM are placed into rD. Use with mulhw for full 64 bit |

- |

| mullw rD,rA,rB |

Multiply Low |

The low-order 32 bits of the 64-bit product (rA)

*(rB) are placed into rD. Use with mulhwu for full 64 bit

mullw. rD,rA,rB mullwo rD,rA,rB mullwo. rD,rA,rB |

- |

| mulhw rD,rA,rB |

Multiply High Word |

The contents of rA and rB are interpreted as 32-bit

signed integers.This gives the top 32 bit of the 64-bit product.

mulhw. rD,rA,rB |

- |

| mulhwu rD,rA,rB |

Multiply High Word Unsigned |

The contents of rA and rB are interpreted as 32-bit

unsigned integers.This gives the top 32 bit of the 64-bit

product.

mulhwu. rD,rA,rB |

- |

| divw rD,rA,rB |

Divide Word |

rD= rA (signed) / rB (signed). To Get Signed

Remainder: divw rD,rA,rB rD = quotient mull rD,rD,rB rD =

quotient*divisor subf rD,rD,rA rD = remainder

divw. rD,rA,rB divwo rD,rA,rB divwo. rD,rA,rB |

- |

| divwu rD,rA,rB |

Divide Word Unsigned |

rD= rA (unsigned) / rB (unsigned). To Get Unsigned

Remainder: divwu rD,rA,r8 rD = quotient mull rD,rD,r8 rD =

quotient*divisor subf rD,rD,rA rD = remainder

divwu. rD,rA,rB divwuo rD,rA,rB divwuo. rD,rA,rB |

- |

| Opcode |

Integer Compare Instructions |

Details i=immediate w=word |

|

| cmp crfD,L,rA,rB |

Compare (Signed) |

CoMPare signed rA with signed rB, storing results

in CR field crfD. L=Length (32/64 bits)

cmpi crfD,L,rA,SIMM cmpw crfD,rA,rB (cmp crfD,O,rA,rB) cmpwi

crfD,rA,SIMM (cmpi crfD,O,rA,SIMM) |

- |

| cmpl crfD,L,rA,rB |

Compare Logical (unsigned) |

CoMPare unsigned rA with unsigned rB, storing

results in CR field crfD. L=Length (32/64 bits)

cmpli crfD,L,rA,UIMM cmplwi crfD,rA,UIMM (cmpli crfD,O,rA,UIMM)

cmplw crfD,rA,rB (cmpl crfD,O,rA,rB) |

- |

| Opcode |

Integer Logical Instructions |

Details .=updateCR i=immediate s=shifted

c=complement / b=byte h=half |

|

| and rA,rS,rB |

AND |

The contents of rS is ANDed with the contents of

register rB and the result is placed into rA.

and. rA,rS,rB andi. rA,rS,UIMM andis. rA,rS,UIMM andc rA,rS,rB

andc. rA,rS,rB |

- |

| or rA,rS,rB |

OR |

The contents of rS is ORed with the contents of rB

and the result is placed into rA.

or. rA,rS,rB ori rA,rS,UIMM oris rA,rS,UIMM orc rA,rS,rB orc.

rA,rS,rB |

- |

| xor rA,rS,rB |

XOR |

The contents of rS is XORed with the contents of rB

and the result is placed into register rA.

xor. rA,rS,rB xori rA,rS,UIMM xoris rA,rS,UIM |

- |

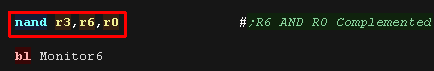

| nand rA,rS,rB |

NAND |

The contents of rS is ANDed with the contents of rB

and the one's complement of the result is placed into register

rA. NAND with rA=rB can be used to obtain the one's complement.

nand. rA,rS,rB |

- |

| nor rA,rS,rB |

NOR |

The contents of rS is ORed with the contents of rB

and the one's complement of the result is placed into register

rA.

nor. rA,rS,rB |

- |

| eqv rA,rS,rB |

Equivalent |

The contents of rS is XORed with the contents of rB

and the complemented result is placed into register rA.

eqv. rA,rS,rB |

- |

extsb rA,rS

extsh rA,rS |

Extend Sign Byte / Halfword |

Register r S[24-31] are placed into rA[24-31]. Bit

24 of rS is placed into rA[O-23].

extsb. rA,rS extsh. rA,rS |

- |

| cntlzw rA,rS |

Count Leading Zeros Word |

Count of leading zero bits of rS is placed into rA.

This number ranges from 0 to 32, inclusive.

cntlzw. rA,rS |

- |

| Opcode |

Integer Rotate Instructions |

Details .=updateCR |

|

| rlwinm rA,rS,SH,MB,ME |

Rotate Left Word Immediate then AND with Mask |

Rotate rS left by SH bits, and keep (AND) bits

MB-ME, storing results in rA

EG: rlwinm r3,r4,8,24,31 will shift R4<<8 and keep bits

24-31 (0=MSB 31=LSB)

rlwinm. rA,rS,SH,MB,ME |

- |

| rlwnm rA,rS,rB,MB,ME |

Rotate Left Word then AND with Mask |

Rotate rS left by rB bits, and keep (AND) bits

MB-ME, storing results in rA

EG: rlwinm r3,r4,8,24,31 will shift R4<<8 and keep bits

24-31 (0=MSB 31=LSB)

rlwnm. rA,rS,rB,MB,ME |

- |

| rlwimi rA,rS,SH,MB,ME |

Rotate Left Word Immediate then Mask Insert |

Rotate rS left by SH bits, and transfer bits MB-ME

into rA (leaving other bits unchanged)

EG: rlwinmi r3,r4,8,24,31 will shift R4<<8 and transfer

bits 24-31 (0=MSB 31=LSB) to R3, bits 0-23 of R3 are unchanged

rlwimi. rA,rS,SH,MB,ME |

- |

| Opcode |

Integer Shift Instructions |

Details .=updateCR |

|

| slw rA,rS,rB |

Shift Left Word |

rS is shifted left rB bits. Bits shifted out are

lost. new bits on the right are 0.

slw. rA,rS,rB |

- |

| srw rA,rS,rB |

Shift Right Word (Unigned) |

rS is shifted right rB bits. New bits on the left

are 0.

srw. rA,rS,rB |

- |

| srawi rA,rS,SH |

Shift Right Algebraic Word Immediate (Signed) |

rS is right SH bits. Bits shifted out are lost. New

bits on the left retain the old top bit, keeping the sign.

XER[CA] is set if r S contains a negative number and any 1-bits

are shifted out of position 3, otherwise XER(CA) is cleared.

srawi. rA,rS,SH |

- |

| sraw rA,rS,rB |

Shift Right Algebraic Word (Signed) |

rS is shifted right rB[26-31] bits. New bits on the

left retain the old top bit, keeping the sign. XER[CA] is set to

1 if rS contains a negative number and any 1-bits are shifted

out of position 31; otherwise XER[CA] is cleared to O. A If

rB[26]= 1, then rA is filled with 32 sign bits (bit 0) from rS.

Condition register field CRO is set based on the value written

into rA.

sraw. rA,rS,rB |

- |

| Opcode |

Integer Load Instructions |

Details b=byte h=half w=word / z=zero extend

(unsigned) a=algebraic (Sign extended) u=update x=indexed |

|

| Ibz rD,d(rA) |

Load Byte and Zero |

Load and zero extend an 8 bit byte from the

effective address.

lbzx rD,rA,rB lbzu rD,d(rA) lbzux rD,rA,rB |

Y |

| lhz rD,d(rA) |

Load Half Word and Zero |

Load and zero extend a 16 bit half word from the

effective address.

lhzx rD,rA,rB lhzu rD,d(rA) lhzux rD,rA,rB |

Y |

| Iha rD,d(rA) |

Load Half Word Algebraic |

Load and sign extend an 16 bit half word from the

effective address.

Ihax rD,rA,rB Ihau rD,d(rA) Ihaux rD,rA,rB |

Y |

| Iwz rD,d(rA) |

Load Word and Zero |

The effective address is the sum (rAI0)+d. The word

in memory addressed by the EA is loaded into register rD[0-31].

lwzx rD,rA,rB lwzu rD,d(rA) lwzux rD,rA,rB |

Y |

| Opcode |

Integer Store Instructions |

Details b=byte h=half w=word / x=indexed u=update |

|

| stb rS,d(rA) |

Store Byte |

The effective address is the sum (rA|0) + d.

Register rS[24�31] is stored into the byte in memory addressed

by the EA.

stbx rS,rA,rB stbu rS,d(rA) stbux rS,rA,rB |

Y |

| sth rS,d(rA) |

Store Half word |

The effective address is the sum (rAIO)+d.

rS[16-31] is stored into the half-word in memory addressed by

the EA.

sthx rS,rA,rB sthu rS,d(rA) sthux rS,rA,rB |

Y |

| stw rS,d(rA) |

Store Word |

The effective address is the sum (rAIO)+d. Register

rS is stored into the word in memory addressed by the EA.

stwx rS,rA,rB stwu rS,d(rA) stwux rS,rA,rB |

Y |

| PsuedoOps |

Miscellaneous Simplified Mnemonics |

Details |

|

| no-op |

No-Op |

(equivalent to ori 0,0,0) |

- |

| li rD,value |

Load Immediate |

Load a 16-bit signed immediate value into rA

(equivalent to addi rA,0,value) |

- |

| lis rD,value |

Load Shifted Immediate |

Load a 16-bit signed immediate value, shifted left

by 16 bits, into rA (equivalent to addis rA,0,value) |

- |

| la rD,SIMM(rA) |

Load Address |

equivalent to addi rD,rA,SIMM |

- |

| la rD,v |

Load Address |

Load Effective addres of Base+Offset (equivalent to

addi rD,rA,SIMM) |

- |

| mr rA,rS |

Move Register |

(equivalent

to or rA,rS,rS) |

- |

| not rA,rS |

Complement Register |

(equivalent to nor rA,rS,rS) |

- |

| sub rD,rA,rB |

|

Equivalent to subf rD,rB,rA |

- |

| subi rD,rA,SIMM |

|

Equivalent to addi rD,rA,-SIMM |

- |

| Opcode |

Integer Load and Store with Byte Reversal

Instructions |

Details |

|

| lhbrx rD,rA,rB |

Load Half Word Byte-Reverse Indexed |

Load unsigned Endian-Reversed 16 bit half into from

(rA+rB). Byte reversed version of LHZX rD,rA,rB |

Y |

| lwbrx rD,rA,rB |

Load Word Byte-Reverse Indexed |

Load Endian-Reversed word into rD from (rA+rB).

This is the Byte reversed version of LWZX rD,rA,rB |

Y |

| sthbrx rS,rA,rB |

Store Half Word Byte-Reverse Indexed |

Store a Endian-Reversed 16 bit half from rD into

(rA+rB). Byte reversed version of STHX rD,rA,rB |

Y |

| stwbrx rS,rA,rB |

Store Word Byte-Reverse Indexed |

Store a Endian-Reversed word from rD into (rA+rB).

This is the Byte reversed version of STWX rD,rA,rB |

Y |

| Opcode |

Integer Load and Store Multiple Instructions |

Details |

|

| Imw rD,d(rA) |

Load Multiple Word (POP) |

The effective address is the sum (rAIO)+d. n=

32-rD. n consecutive words starting at EA are loaded into GPRs

rD through 31. EA should be 32 bit aligned. Used as stack POP |

Y |

| stmw rS,d(rA) |

Store Multiple Word (PUSH) |

The effective address is the sum (rAIO)+d. n=

(32-rS). n consecutive words starting at the EA are stored from

GPRs rS through 31. EA should be 32 bit aligned. Used as stack

PUSH |

Y |

| Opcode |

Integer Move String Instructions |

Details |

|

| Iswi rD,rA,NB |

Load String Word Immediate |

Load NB bytes from source address rA to registers

rD+EG: lswi r4,r3,7#; Load 7 bytes into R4+ from (R3) |

Y |

| Iswx rD,rA,rB |

Load String Word Indexed |

Load XER:ByteCount (low 6 bits) bytes into rD+ from

(rA+rB)EG: lswx r5,r3,r4#; Load XER:ByteCount (low 6 bits) bytes

into R5+ from (R3+R4) |

Y |

| stswi rS,rA,NB |

Store String Word Immediate |

Store NB bytes to destination address rA from

registers rD+EG: stswi r4,r3,7#; Store 7 bytes from R4+ to (R3) |

Y |

| stswx rS,rA,rB |

Store String Word Indexed |

Load XER:ByteCount (low 6 bits) bytes into rD+ from

(rA+rB)EG: stswx r5,r3,r4#; Store XER:ByteCount (low 6 bits)

bytes from R5+ to (R3+R4) |

Y |

| Opcode |

Branch Instructions |

Details |

|

| b imm_addr |

Branch. |

Branch to the address imm_addr |

- |

| ba imm_addr |

Branch Absolute. |

Branch to the absolute address specified. |

- |

| bl imm_addr |

Branch then Link. |

Branch to subroutine, and put return address in the

Link Register (LR). |

- |

| bla imm_addr |

Branch Absolute then Link. |

Branch to subroutine at absolute address, and put

return address in the Link Register (LR). |

- |

| bc BO,BI,target_addr |

Branch Conditional. |

Branch conditionally to the address computed as the

sum of the immediate address and the address of the current

instruction. The BI operand specifies the bit in the condition

register (CR) to be used |

- |

| bca BO,BI,target_addr |

Branch Conditional Absolute. |

Branch conditionally to the absolute address

specified. |

- |

| bcl BO,BI,target_addr |

Branch Conditional then Link. |

Branch conditionally to the address computed as the

sum of the immediate address and the address of the current

instruction. The instruction address following this instruction

is placed into the link register. |

- |

| bcla BO,BI,target_addr |

Branch Conditional Absolute then Link. |

Branch conditionally to the absolute address

specified. The instruction address following this instruction is

placed into the link register. |

- |

| bclr BO,BI |

Branch Conditional to Link Register |

Branch Conditional to Link Register. Branch

conditionally to the address in the link register.

The BI operand specifies the bit in the condition register to be

used belrl as the condition of the branch. |

- |

| bclrl BO,BI |

Branch Conditional to Link Register then Link. |

Branch conditionally to the address specified in

the link register.

The instruction address following this instruction is then

placed into the link register. |

- |

| bcctr BO,BI |

Branch Conditional to Count Register. |

Branch conditionally to the address specified in

the count register. The BI operand specifies the bit in the

condition register to be used as the condition of the branch. |

- |

| bcctrl BO,BI |

Branch Conditional to Count Register then Link. |

Branch conditionally to the address specified in

the count register. The instruction address following this

instruction is placed into the link register. |

- |

| blr |

Branch to Link Register |

Return from sub |

- |

| Opcode (+/-=branch prediction) |

Bcc PsuedoOp |

Details a=Absolute lr=to LinkRegister ctr=to CTR

L=Link |

|

| blt target |

Branch if less than |

blt label blta addr bltlr bltctr bltl label bltla

addr bltlrl bltctrl (Psuedo for bc 12.0.Target) |

- |

| ble target |

Branch if less than or equal |

ble label blea addr blelr blectr blel label blela

addr blelrl blectrl |

- |

| beq target |

Branch if equal |

beq label beqa addr beqlr beqctr beql label beqla

addr beqlrl beqctrl |

- |

| bge target |

Branch if greater than or equal |

ble label blea addr blelr blectr blel label blela

addr blelrl blectrl |

- |

| bgt target |

Branch if greater than |

bgt label bgta addr bgtlr bgtctr bgtl label bgtla

addr bgtlrl bgtctrl |

- |

| bnl target |

Branch if not less than |

bnl label bnla addr bnllr bnlctr bnll label bnlla

addr bnllrl bnlctrl |

- |

| bne target |

Branch if not equal |

bne label bnea addr bnelr bnectr bnel label bnela

addr bnelrl bnectrl (Psuedo for bc 4.2.Target) |

- |

| bng target |

Branch if not greater than |

bng label bnga addr bnglr bngctr bngl label bngla

addr bnglrl bngctrl |

- |

| bso target |

Branch if summary overflow |

bso label bsoa addr bsolr bsoctr bsol label bsola

addr bsolrl bsoctrl |

- |

| bns target |

Branch if not summary overflow |

bns label bnsa addr bnslr bnsctr bnsl label bnsla

addr bnslrl bnsctrl |

- |

| bun target |

Branch if unordered |

bun label buna addr bunlr bunctr bunl label bunla

addr bunlrl bunctrl |

- |

| bnu target |

Branch if not unordered |

bnu label bnua addr bnulr bnuctr bnul label bnula

addr bnulrl bnuctrl |

- |

| Opcode |

Bcc PsuedoOp |

Details a=Absolute lr=to LinkRegister ctr=to CTR

l=Link |

|

| bt cond,target |

Branch if Condition True |

bta btlr btctr btl btla btlrl btctrl |

- |

| bf cond,target |

Branch if Condition False |

bfa bflr bfctr bfl bfla bflrl bfctrl |

- |

| bdnz target |

Branch after Decrement if nonzero |

Decrement Count Register CTR, branch if CTR nonzero

bdnza bdnzlr bdnzl bdnzla bdnzlrl |

- |

| bdnzt cond,target |

Branch after Decrement if nonzero and condition

cond TRUE |

Decrement Count Register CTR, branch if CTR nonzero

AND condition true (cond=LT/GT/EQ/SO/UN)

bdnzta bdnztlr bdnztl bdnztla bdnztlrl |

- |

| bdnzf cond,target |

Branch after Decrement if nonzero and condition

cond FALSE |

Decrement Count Register CTR, branch if CTR nonzero

AND condition false (cond=LT/GT/EQ/SO/UN)

bdnzfa bdnzflr bdnzfl bdnzfla bdnzflrl |

- |

| bdz target |

Branch after Decrement if zero |

Decrement Count Register CTR, branch if CTR zero

bdza bdzlr bdzl bdzla bdzlrl |

- |

| bdzt cond,target |

Branch after Decrement if zero and condition cond

TRUE |

Decrement Count Register CTR, branch if CTR zero

AND condition true

bdzta bdztlr bdztl bdztla bdztlrl |

- |

| bdzf cond,target |

Branch after Decrement if zero and condition cond

FALSE |

Decrement Count Register CTR, branch if CTR zero

AND condition false

bdzfa bdzflr bdzfl bdzfla bdzflrl |

- |

| Opcode |

Condition Register Logical Instructions |

Details |

|

| crand crbD,crbA,crbB |

Condition Register AND |

single bit crbA is ANDed with crbB and stored in

crbD. |

- |

| cror crbD,crbA,crbB |

Condition Register OR |

single bit crbA is ORed with crbB and stored in

crbD. |

- |

| crxor crbD,crbA,crbB |

Condition Register XOR |

single bit crbA is XORed with crbB and stored in

crbD. |

- |

| crnand crbD,crbA,crbB |

Condition Register NAND |

single bit crbA is ANDed with crbB and the

complement (NOT) is stored in crbD. |

- |

| crnor crbD,crbA,crbB |

Condition Register NOR |

single bit crbA is ORed with crbB and the

complement (NOT) is stored in crbD. |

- |

| creqv crbD,crbA,crbB |

Condition Register Equivalent |

single bit crbA is CORed with crbB and the

complement (NOT) is stored in crbD. |

- |

| crandc crbD,crbA,crbB |

Condition Register AND with Complement |

single bit crbA is ANDed with the compliment (bit

flipped) of crbB and stored in crbD. |

- |

| crorc crbD,crbA,crbB |

Condition Register OR with Complement |

single bit crbA is ORed with the compliment (bit

flipped) of crbB and stored in crbD. |

- |

| mcrf crfD,crfS |

Move Condition Register Field |

The contents of crfS are copied into crfD. No other

condition register fields are changed. |

- |

| Opcode |

System Linkage Instructions |

Details |

|

| sc |

System Call |

|

- |

| rfi |

Return from Interrupt |

|

- |

| Opcode |

Trap Instructions and Mnemonics |

Details |

|

| twi TO,rA,SIMM |

Trap Word Immediate |

Trap if condition TO comparing rA to SIMM

(TO=01/2/3/4=LT/GT/EQ/LogicalLT/LogicalGT)

twlti rA,SIMM twlei rA,SIMM tweqi rA,SIMM twgei rA,SIMM twgti

rA,SIMM twnli rA,SIMM

twnei rA,SIMM twllti rA,SIMM twngi rA,SIMM twllti rA,SIMM twllei

rA,SIMM twlgei rA,SIMM

twlgti rA,SIMM twlnli rA,SIMM twlngi rA,SIMM |

- |

| tw TO,rA,rB |

Trap Word |

Trap if condition TO comparing rA to RB

(TO=01/2/3/4=LT/GT/EQ/LogicalLT/LogicalGT)

twlt rA,rB twle rA,rB tweq rA,rB twge rA,rB twgt rA,rB twnl

rA,rB twne rA,rB twllt rA,rB twng rA,rB

twllt rA,rB twlle rA,rB twlge rA,rB twlgt rA,rB twlnl rA,rB

twlng rA,rB |

- |

| Opcode |

Move to/from Machine State Register/Condition

Register Instructions |

Details |

|

| mtcrf CRM,rS |

Move to Condition Register Fields |

CRM=bits 0-7... eg 0xFF=all CRM fields |

- |

| mcrxr crfD |

Move to Condition Register |

Move from XER bits 0-3 (SO OV CA --), Clear these

bits in XER |

- |

| mfcr rD |

Move from Condition Register |

|

- |

| mtmsr rS |

Move to Machine State Register |

|

- |

| mfmsr rD |

Move from Machine State Register |

|

- |

| Opcode |

Cache Management Supervisor-Level Instruction |

Details |

|

| dcbi rA,rB |

Data Cache Block Invalidate |

|

- |

| Opcode |

User-Level Cache Instructions |

Details |

|

| dcbt rA,rB |

Data Cache Block Touch |

|

- |

| dcbtst rA,rB |

Data Cache Block Touch for Store |

|

- |

| clcs rD,rA |

Cache Line Compute Size |

|

- |

| dcbz rA,rB |

Data Cache Block Set to Zero |

|

- |

| dcbst rA,rB |

Data Cache Block Store |

|

- |

| dcbf rA,rB |

Data Cache Block Flush |

|

- |

| Opcode |

Move to/from Special Purpose Register Instructions |

Details |

|

| mtspr SPR,rS |

Move to Special Purpose Register |

Transfer rS to SPR (MQ,XER,RTCU,RTCL,DEC,LR,CTR).

Simplified versions exist:

mtxer rA mtspr 1,rA mtlr rA mtspr 8,rA mtctr rA mtspr 9,rA |

- |

| mfspr rD,SPR |

Move from Special Purpose Register |

Transfer Special SPR to rD.

(MQ,XER,RTCU,RTCL,DEC,LR,CTR). Simplified versions exist:

mfxer rA mfspr rA,1 mflr rA mfspr rA,8 mfctr rA mfspr rA,9 |

- |

| Opcode |

Segment Register Manipulation Instructions |

Details |

|

| mtsr SR,rS |

Move to Segment Register |

The contents of rS is placed into segment register

specified by operand SR. (Supervisor instruction) |

- |

| mtsrin rS,rB |

Move to Segment Register Indirect |

The contents of rS are copied to the segment

register selected by bits 0�3 of rB. (Supervisor instruction) |

- |

| mfsr rD,SR |

Move from Segment Register |

The contents of the segment register specified by

operand SR are placed into rD. (Supervisor instruction) |

- |

| mfsrin rD,rB |

Move from Segment Register Indirect |

The contents of the segment register selected by

bits 0�3 of rB are copied into rD. (Supervisor instruction) |

- |

| Opcode |

Translation Lookaside Buffer Management Instruction |

Details |

|

| tlbie rB |

Translation Lookaside Buffer Invalidate Entry |

|

- |

| Opcode |

External Control Instructions |

Details |

|

| eciwx rD,rA,rB |

External Control Input Word Indexed |

|

Y |

| ecowx rS,rA,rB |

External Control Output Word Indexed |

|

Y |

| Opcode |

Memory Synchronization Instructions |

Details |

|

| eieio |

Enforce In�Order Execution of I/O |

|

- |

| isync |

Instruction Synchronize |

|

- |

| Iwarx rD,rA,rB |

Load Word and Reserve Indexed |

|

- |

| stwcx. rS,rA,rB |

Store Word Conditional Indexed |

|

- |

| sync |

Synchronize |

|

- |